Technical Description

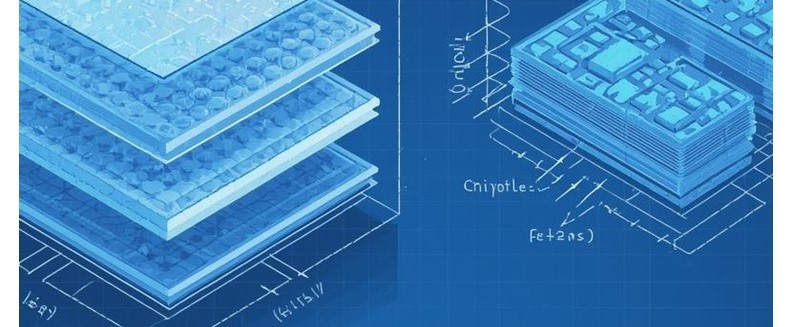

The present invention pertains to thin film transistors with a multi-finger or Corbino source/drain architecture to accommodate a large channel width in a limited layout space.

Problems Addressed

- Complicated Process

- Inefficient Performance

- Low Transconductance

- Suboptimal Architecture

Tech Features

- High Transconductance

- Simpler Process

- Large Channel Accommodation

- Infinite Output Resistance

- Optimized Architecture

- Current Leakage Reduction

- Constant Current Source

Target Audience

- Consumer Electronics Industry

- Automotive Sector

- Telecommunications Industry

- Research & Development

Tech ID: P16-1799 TRL 4 Patent Status: Published Available For Exclusive and Non-exclusive License

×

P16-1799

DOWNLOAD

Send download link to email.